Alan Clements

# COMPUTER ORGANIZATION AND ARCHITECTURE

Themes and Variations

**Alan Clements**

**Teesside University**

This is an electronic version of the print textbook. Due to electronic rights restrictions, some third party content may be suppressed. Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. The publisher reserves the right to remove content from this title at any time if subsequent rights restrictions require it. For valuable information on pricing, previous editions, changes to current editions, and alternate formats, please visit <a href="www.cengage.com/highered">www.cengage.com/highered</a> to search by ISBN#, author, title, or keyword for materials in your areas of interest.

#### **Computer Organization and Architecture:** Themes and Variations, First Edition **Alan Clements**

Publisher, Global Engineering: Christopher M.

Shortt

Acquisitions Editor: Swati Meherishi

Developmental Editor: Amy Hill, Collaborative

Concepts, LLC

Assistant Development Editor: Farah Naseem

Editorial Assistant: Tanya Altieri Team Assistant: Carly Rizzo

Marketing Manager: Lauren Betsos

Media Editor: Chris Valentine

Content Project Manager: D. Jean Buttrom Production Service: RPK Editorial Services, Inc.

Copyeditor: Shelly Gerger-Knechtl

Proofreader: Pat Daly

Indexer: Shelly Gerger-Knechtl Compositor: MPS Limited

Senior Art Director: Michelle Kunkler

Cover and Internal Designer: Rokusek Design

Cover Image: © Dvpodt/Shutterstock

Rights Acquisition Director: Audrey Pettengill

Rights Acquisition Specialist, Text and Image:

Amber Hosea

Text and Image Permissions Researcher:

Kristiina Paul

Senior Manufacturing Planner: Doug Wilke

#### © 2014 Cengage Learning

ALL RIGHTS RESERVED. No part of this work covered by the copyright herein may be reproduced, transmitted, stored, or used in any form or by any means graphic, electronic, or mechanical, including but not limited to photocopying, recording, scanning, digitizing, taping, web distribution, information networks, or information storage and retrieval systems, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without the prior written permission of the publisher.

> For product information and technology assistance, contact us at Cengage Learning Customer & Sales Support, 1-800-354-9706.

For permission to use material from this text or product, submit all requests online at www.cengage.com/permissions. Further permissions questions can be emailed to permissionrequest@cengage.com.

Library of Congress Control Number: 2012942868

ISBN-13: 978-1-111-98704-6

ISBN-10: 1-111-98704-1

#### **Cengage Learning**

200 First Stamford Place, Suite 400

Stamford, CT 06902

USA

Cengage Learning is a leading provider of customized learning solutions with office locations around the globe, including Singapore, the United Kingdom, Australia, Mexico, Brazil, and Japan. Locate your local office at:

international.cengage.com/region.

Cengage Learning products are represented in Canada by Nelson Education Ltd.

For your course and learning solutions, visit www.cengage.com/engineering.

Purchase any of our products at your local college store or at our preferred online store www.cengagebrain.com.

# Dedication

Dedicated to the memory of my friend, colleague, and mentor Tomás López Jiménez.

# **Contents**

Paths through Computer Architecture

Preface

| PART I | THE | BEGINNING                                   | "IISC M | \$ 1 |

|--------|-----|---------------------------------------------|---------|------|

| 1      | Cor | mputer Systems Architecture                 | 6       |      |

|        |     | Where We're At                              | 7       |      |

|        | 1.1 | What is Computer Systems Architecture?      | 9       |      |

|        |     | What is a Computer?                         | 11      |      |

|        | 1.2 | Architecture and Organization               | 14      |      |

|        |     | 1.2.1 Computer Systems and Technology       | 17      |      |

|        |     | 1.2.2 The Role of Computer Architecture     |         |      |

|        |     | in Computer Science                         | 19      |      |

|        | 1.3 | Development of Computers                    | 21      |      |

|        |     | 1.3.1 Mechanical Computers                  | 21      |      |

|        |     | 1.3.2 Electromechanical Computers           | 24      |      |

|        |     | 1.3.3 Early Electronic Computers            | 24      |      |

|        |     | 1.3.4 Minicomputers and the PC Revolution   | 25      |      |

|        |     | 1.3.5 Moore's Law and the March of Progress | 25      |      |

|        |     | 1.3.6 The March of Memory Technology        | 26      |      |

|        |     | 1.3.7 Ubiquitous Computing                  | 27      |      |

|        |     | 1.3.8 Multimedia Computers                  | 28      |      |

|        | 1.4 | The Stored Program Computer                 | 28      |      |

|        |     | 1.4.1 The Problem                           | 29      |      |

|        |     | 1.4.2 The Solution                          | 29      |      |

|        |     | 1.4.3 Constructing an Algorithm             | 31      |      |

1.4.4 What Does a Computer Need to Solve a Problem?

1.4.5 The Memory

1.6.2 The Bus

1.7 Modern Computing

2.1 What is Data?

Summary **Problems**

1.5 The Stored Program Concept

Two Address Instructions

One Address Instructions

Computer Categories 1.6 Overview of the Computer System

**Computer Arithmetic and Digital Logic**

Representing Information

2.1.1 The Bit and Byte

2.1.2 Bit Patterns

1.6.1 The Memory Hierarchy

xix

32

34

37

39

40 40

41

41

43

45 46

46

48

50

50

51 51 11500

xxix

| 2.2  | Numb    | ers                                            | 55       |

|------|---------|------------------------------------------------|----------|

|      | 2.2.1   | Positional Notation                            | 56       |

| 2.3  | Binary  | Arithmetic                                     | 57       |

| 2.4  | Signed  | d Integers                                     | 59       |

|      | 2.4.1   | Sign and Magnitude Representation              | 60       |

|      | 2.4.2   | Two's Complement Arithmetic                    | 60       |

|      |         | Calculating Two's Complement Values            | 61       |

|      |         | Properties of Two's Complement Numbers         | 62       |

|      |         | Arithmetic Overflow                            | 62       |

| 2.5  | Introd  | uction to Multiplication and Division          | 63       |

|      | 2.5.1   | Shifting Operations                            | 63       |

|      | 2.5.2   | Unsigned Binary Multiplication                 | 64       |

|      | 2.5.3   | High-speed Multiplication                      | 64       |

|      |         | Booth's Algorithm                              | 66       |

|      | 2.5.4   | Division                                       | 67       |

|      |         | Restoring Division                             | 68       |

|      |         | Non-Restoring Division                         | 70       |

| 2.6  | Floatir | ng-Point Numbers                               | 71       |

|      |         | Normalization of Floating-Point Numbers        | 72       |

|      |         | Biased Exponents                               | 72       |

|      | 2.6.1   | IEEE Floating-Point Numbers                    | 72       |

|      | 2.0.1   | IEEE Floating-Point Format                     | 73       |

|      |         | Characteristics of IEEE Floating-Point Numbers | 75       |

| 2.7  | Floatir | ng-Point Arithmetic                            | 77       |

| ,    | Houth   | Rounding and Truncation Errors                 | 78       |

| 2.8  | Floatir | ng-Point Arithmetic and the Programmer         | 79       |

| 2.0  | 2.8.1   | Error Propagation in Floating-Point Arithmetic | 81       |

|      | 2.8.2   | Generating Mathematical Functions              | 81       |

|      | 2.0.2   | Using Functions to Generate New Functions      | 83       |

| 2.9  | Comp    | uter Logic                                     | 84       |

| 2.,  | 2.9.1   | Digital Systems and Gates                      | 86       |

|      | 2.9.2   | Gates                                          | 86       |

|      | 2.7.2   | Fundamental Gates                              | 87       |

|      |         | The AND Gate                                   | 87       |

|      |         | The OR Gate                                    | 87       |

|      |         | The Inverter                                   | 88       |

|      |         |                                                | oc       |

|      |         | Derived Gates—the NOR (Not OR), NAND           | 90       |

|      | 2.9.3   | (Not AND), and Exclusive OR Basic Circuits     | 89<br>91 |

|      | 2.9.3   | The Half Adder and Full Adder                  | 91       |

|      |         |                                                | 93       |

|      |         | The Decoder                                    | 97       |

|      |         | The Multiplexer                                |          |

|      |         | The Point Circuit                              | 98       |

| 2 10 | Comus   | The Prioritizer                                | 100      |

| 2.10 | -       | ntial Circuits                                 | 101      |

|      | ∠.1∪.1  | Latches Clocked BS Flin floor                  | 102      |

|      |         | Clocked RS Flip-flops                          | 104      |

|      |         | D Flip-flop                                    | 105      |

|      | 2 10 2  | The JK Flip-Flop                               | 108      |

|      | 2.10.2  | Registers                                      | 109      |

|      |         | Shift Register                                 | 110      |

|      |         | Left-Shift Register                            | 111      |

| 2.10.3 Asynchronous Counters           | 113 |

|----------------------------------------|-----|

| Using a Counter to Create a Sequencer  | 114 |

| 2.10.4 Sequential Circuits             | 115 |

| 2.11 Buses and Tristate Gates          | 118 |

| Registers, Buses, and Functional Units | 120 |

| Summary                                | 122 |

| Problems                               | 123 |

|                                        |     |

| PART II | INSTRUCTION SET ARCHITECTURES |        |                                                  |     |  |  |  |

|---------|-------------------------------|--------|--------------------------------------------------|-----|--|--|--|

| 3       | Arc                           | hitect | ure and Organization                             | 130 |  |  |  |

|         | 3.1                           | Intro  | duction to the Stored Program Machine            | 130 |  |  |  |

|         |                               | 3.1.1  | Extending the Processor: Dealing with Constants  | 136 |  |  |  |

|         |                               | 3.1.2  | Extending the Processor: Flow Control            | 139 |  |  |  |

|         |                               |        | Status Information                               | 141 |  |  |  |

|         |                               |        | Example of a Branch Instruction                  | 142 |  |  |  |

|         | 3.2                           | The C  | omponents of an ISA                              | 146 |  |  |  |

|         |                               | 3.2.1  | Registers                                        | 146 |  |  |  |

|         |                               |        | General-Purpose Versus Special-Purpose Registers | 147 |  |  |  |

|         |                               | 3.2.2  | Addressing Modes—an Overview                     | 149 |  |  |  |

|         |                               |        | Memory and Register Addressing                   | 151 |  |  |  |

|         |                               | 3.2.3  | Instruction Formats                              | 151 |  |  |  |

|         |                               | 3.2.4  | Op-codes and Instructions                        | 152 |  |  |  |

|         |                               |        | Two Address Machines                             | 153 |  |  |  |

|         |                               |        | One Address Machines                             | 153 |  |  |  |

|         |                               |        | Zero Address Machines                            | 153 |  |  |  |

|         |                               |        | One-and-a-Half Address Machines                  | 154 |  |  |  |

|         | 3.3                           | ARM    | Instruction Set Architecture                     | 155 |  |  |  |

|         |                               | 3.3.1  | ARM's Register Set                               | 156 |  |  |  |

|         |                               | 3.3.2  | ARM's Instruction Set                            | 156 |  |  |  |

|         | 3.4                           | ARM A  | Assembly Language                                | 157 |  |  |  |

|         |                               | 3.4.1  | Structure of an ARM Program                      | 158 |  |  |  |

|         |                               | 3.4.2  | The Assembler – Practical Considerations         | 161 |  |  |  |

|         |                               | 3.4.3  | Pseudoinstructions                               | 164 |  |  |  |

|         | 3.5                           | ARM    | Data-processing Instructions                     | 167 |  |  |  |

|         |                               | 3.5.1  | Arithmetic Instructions                          | 167 |  |  |  |

|         |                               |        | Addition and Subtraction                         | 167 |  |  |  |

|         |                               |        | Negation                                         | 168 |  |  |  |

|         |                               |        | Comparison                                       | 168 |  |  |  |

|         |                               |        | Multiplication                                   | 169 |  |  |  |

|         |                               |        | Division                                         | 170 |  |  |  |

|         |                               | 3.5.2  | Bitwise Logical Operations                       | 170 |  |  |  |

|         |                               | 3.5.3  | Shift Operations                                 | 171 |  |  |  |

|         |                               |        | Arithmetic Shift                                 | 173 |  |  |  |

|         |                               |        | Rotate                                           | 173 |  |  |  |

|         |                               |        | Implementing a Shift Operation on the ARM        | 173 |  |  |  |

|         |                               | 3.5.4  | Instruction Encoding—An Insight Into             |     |  |  |  |

|         |                               |        | the ARM's Architecture                           | 175 |  |  |  |

|         | 3.6                           | ARM'   | s Flow Control Instructions                      | 176 |  |  |  |

|         |                               | 3.6.1  | Unconditional Branch                             | 176 |  |  |  |

|         |                               | 3.6.2  | Conditional Branch                               | 177 |  |  |  |

|      |        | Compare and Test Instructions Branching and Loop Constructs                | 178<br>178 |

|------|--------|----------------------------------------------------------------------------|------------|

|      | 3.0.4  | -                                                                          | 178<br>178 |

|      |        | The FOR Loop                                                               | 178<br>178 |

|      |        | The UNITH loop                                                             | 178<br>179 |

|      |        | The UNTIL loop                                                             | 179<br>179 |

|      | 3.6.5  | Combination Loop Conditional Execution                                     | 179        |

| 3.7  |        | Addressing Modes                                                           | 1/9        |

| 3./  |        | Literal Addressing                                                         | 182        |

|      | 3.7.1  | ARM's Way                                                                  | 183        |

|      | 372    | Register Indirect Addressing                                               | 184        |

|      |        |                                                                            | 187        |

|      |        | Register Indirect Addressing with an Offset ARM's Autoindexing Pre-indexed | 167        |

|      | 3.7.4  |                                                                            | 190        |

|      | 275    | Addressing Mode ARM's Autoindexing Post-Indexing Mode                      | 190        |

|      |        |                                                                            | 191        |

|      | 3.7.0  | Program Counter Relative (PC-Relative) Addressing                          | 192        |

|      | 277    | ARM's Load and Store Encoding                                              | 192        |

| 3.8  |        | utine Call and Return                                                      | 193        |

| 3.0  |        | ARM Support for Subroutines                                                | 194        |

|      | 3.8.2  | **                                                                         | 190        |

| 3.9  | ···    | nission: Examples of ARM Code                                              | 197        |

| 3.9  |        | Extracting the Absolute Value                                              | 198        |

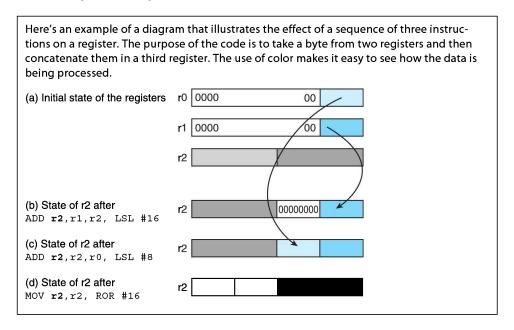

|      |        | Byte Manipulation and Concatenation                                        | 198        |

|      |        | Byte Reversal                                                              | 198        |

|      |        | Multiplication by $2^n - 1$ or $2^n + 1$                                   | 200        |

|      |        | The Use of Multiple Conditions                                             | 200        |

|      |        | •                                                                          | 200        |

|      |        | Implementing Multiple Selection                                            | 200        |

|      |        | Simple Bit-Level Logical Operations                                        | 201        |

|      |        |                                                                            | 201        |

|      |        | Character Output in Hexadecimal                                            | 201        |

|      |        | To Print a Banner                                                          | 202        |

| 2 10 |        | utines and the Stack                                                       | 202        |

| 3.10 |        | Subroutine Call and Return                                                 | 205        |

|      |        | Nested Subroutines                                                         | 206        |

|      |        | Leaf Routines                                                              | 207        |

| 2 11 |        | size and Arrangement                                                       | 209        |

| J.11 |        | Data Organization and Endianism                                            | 209        |

|      |        | Data Organization and the ARM                                              | 211        |

|      |        | Block Move Instructions                                                    | 216        |

|      | 3.11.3 | Block Moves and Stack Operations                                           | 217        |

|      |        | Applications of Block Move Instructions                                    | 219        |

| 3.12 | Conso  | lidation—Putting Things Together                                           | 220        |

| J.12 | COIISO | Four-Function Calculator Program                                           | 220        |

| Sum  | mary   | 1 out 1 direction Culvatator 1 logiani                                     | 223        |

|      | lems   |                                                                            | 224        |

|      |        |                                                                            |            |

| Inst | ructio | n Set Architectures—Breadth and Depth                                      | 228        |

Historical Background

230

4

| 4.1  | The S   | tack and Data Storage                   | 231        |

|------|---------|-----------------------------------------|------------|

|      | 4.1.1   | Storage and the Stack                   | 232        |

|      |         | The Stack Frame and Local Variables     | 234        |

|      |         | Example of an ARM Processor Stack Frame | 237        |

|      | 4.1.2   | <u>*</u>                                | 239        |

|      |         | Pointers and C                          | 242        |

|      |         | Functions and Parameters                | 243        |

|      |         | Pass-by-Reference                       | 246        |

|      |         | Using Recursion                         | 248        |

| 4.2  | Privil  | eged Modes and Exceptions               | 251        |

| 4.3  |         | : Another RISC                          | 254        |

|      |         | MIPS Instruction Format                 | 255        |

|      |         | Conditional Branches                    | 256        |

|      | 4.3.1   | MIPS Data Processing Instructions       | 257        |

|      | 1.5.1   | Flow Control                            | 258        |

|      |         | MIPS Example                            | 259        |

|      |         | Other Loads and Stores                  | 259        |

|      |         | MIPS and the ARM Processor              | 259        |

| 4.4  | Data    | Processing and Data Movement            | 260        |

| •••  |         | Indivisible Exchange Instructions       | 263        |

|      |         | Double-Precision Shifting               | 264        |

|      |         | Pack and Unpack Instructions            | 265        |

|      |         | Bounds Testing                          | 266        |

|      |         | Bit Field Data                          | 268        |

|      | 4.4.6   | Mechanizing the Loop                    | 272        |

| 4.5  |         | ory Indirect Addressing                 | 273        |

| 7.5  | Wicini  | Using Memory Indirect Addressing to     | 273        |

|      |         | Implement a switch Construct            | 277        |

|      |         | Using Memory Indirect Addressing to     | 211        |

|      |         | Access Records                          | 280        |

| 4.6  | Comr    | pressed Code, RISC, Thumb, and MIPS16   | 282        |

| 7.0  | 4.6.1   | Thumb ISA                               | 282        |

|      | 7.0.1   | Design Decisions                        | 283        |

|      | 4.6.2   | MIPS16                                  | 287        |

| 4.7  |         | ble-Length Instructions                 | 288        |

| 7.7  | varia   | Decoding Variable-Length Instructions   | 292        |

| Sum  | mary    | Decoding variable-Length instructions   | 292<br>294 |

|      | olems   |                                         | 294        |

| FIUL | JICIIIS |                                         | 294        |

|      |         |                                         |            |

| Con  | npute   | er Architecture and Multimedia          | 298        |

| 5.1  | Appli   | cations of High-Performance Computing   | 299        |

|      |         | Computer Graphics                       | 301        |

|      | 5.1.1   | Operations On Images                    | 303        |

|      |         | Noise Filtering                         | 303        |

|      |         | Contrast Enhancement                    | 303        |

|      |         | Edge Enhancement                        | 304        |

|      |         | Lossy Compression                       | 305        |

|      |         | JPEG                                    | 305        |

|      |         | MPEG                                    | 308        |

|      |         | MP3                                     | 308        |

5

|         |          | 5.3        | Introduction to SIMD Processing                                          | 318                      |

|---------|----------|------------|--------------------------------------------------------------------------|--------------------------|

|         |          |            | Packed Operations                                                        | 319                      |

|         |          |            | Saturating Arithmetic                                                    | 321                      |

|         |          |            | Packed Shifting                                                          | 323                      |

|         |          |            | Packed Multiplication                                                    | 323                      |

|         |          |            | Parallel Comparison                                                      | 324                      |

|         |          |            | Packing and Unpacking                                                    | 325                      |

|         |          |            | Coexisting with Floating-Point                                           | 326                      |

|         |          |            | 5.3.1 Applications of SIMD Technology                                    | 328                      |

|         |          |            | Chroma Keying                                                            | 328                      |

|         |          |            | Fade In and Out                                                          | 330                      |

|         |          |            | Clipping                                                                 | 332                      |

|         |          | 5.4        | Streaming Extensions and the                                             |                          |

|         |          |            | Development of SIMD Technology                                           | 333                      |

|         |          |            | 5.4.1 Floating-point Software Extensions                                 | 336                      |

|         |          |            | 5.4.2 Intel's Third Layer of Multimedia Extensions                       | 338                      |

|         |          |            | 5.4.3 Intel's SSE3 and SSE4 Instructions                                 | 338                      |

|         |          |            | 5.4.4 ARM Family Multimedia Instructions                                 | 340                      |

|         |          | Sum        | mary                                                                     | 342                      |

|         |          |            | lems                                                                     | 343                      |

|         |          |            |                                                                          |                          |

| 1150 1  | PART III | ORG        | SANIZATION AND EFFICIENCY                                                |                          |

| (%H   ¥ |          |            |                                                                          | - 40                     |

|         | 6        | Per        | formance—Meaning and Metrics                                             | 348                      |

|         |          | 6.1        | Progress and Computer Technology                                         | 351                      |

|         |          |            | Moore's Law                                                              | 351                      |

|         |          |            | Semiconductor Progress                                                   | 352                      |

|         |          |            | Memory Progress                                                          | 354                      |

|         |          | 6.2        | The Performance of a Computer                                            | 356                      |

|         |          | 6.3        | Computer Metrics                                                         | 358                      |

|         |          |            | 6.3.1 Terminology                                                        | 359                      |

|         |          |            | Efficiency                                                               | 359                      |

|         |          |            | Throughput                                                               | 360                      |

|         |          |            | Latency                                                                  | 360                      |

|         |          |            | Relative Performance                                                     | 360                      |

|         |          |            | Time and Rate                                                            | 361                      |

|         |          |            | 6.3.2 Clock Rate                                                         | 361                      |

|         |          |            | The Clock and the Consumer                                               | 365                      |

|         |          |            | 6.3.3 MIPS                                                               | 365                      |

|         |          |            |                                                                          |                          |

|         |          |            | Instruction Cycles and MIPS                                              | 367                      |

|         |          |            | 6.3.4 MFLOPS                                                             | 367<br>369               |

|         |          | 6.4        | 6.3.4 MFLOPS<br>Amdahl's Law                                             |                          |

|         |          | 6.4        | 6.3.4 MFLOPS                                                             | 369                      |

|         |          | 6.4<br>6.5 | 6.3.4 MFLOPS Amdahl's Law Examples of the Use of Amdahl's Law Benchmarks | 369<br>371               |

|         |          |            | 6.3.4 MFLOPS Amdahl's Law Examples of the Use of Amdahl's Law            | 369<br><b>371</b><br>372 |

Digital Signal Processing

**Architectural Progress**

5.2 Multimedia Influences—Reinventing the CISC

The SHARC Family of Digital Signal Processors

**DSP** Architectures

309

312

312

314

315

|   |      |        | Oracle Applications Standard Benchmark     | 375 |

|---|------|--------|--------------------------------------------|-----|

|   |      |        | PC Benchmarks                              | 376 |

|   |      |        | Comparison of High-Performance Processors  | 376 |

|   |      |        | PCMARK7 A Commercial Benchmark for PCs     | 378 |

|   | 6.6  | SPEC   |                                            | 382 |

|   |      |        | SPEC Methodology                           | 384 |

|   |      |        | The SPEC CPU2006 Benchmarks                | 386 |

|   |      | _      | SPEC and Power                             | 389 |

|   | 6.7  | Avera  | aging Metrics                              | 391 |

|   |      |        | Geometric Mean                             | 392 |

|   |      |        | Harmonic Mean                              | 393 |

|   | _    |        | Weighted Means                             | 394 |

|   |      | mary   |                                            | 394 |

|   | Prot | olems  |                                            | 395 |

| 7 | Pro  | cesso  | r Control                                  | 398 |

|   | 7.1  | The G  | ieneric Digital Processor                  | 401 |

|   |      | 7.1.1  |                                            | 404 |

|   |      |        | Modifying the Processor Organization       | 406 |

|   |      | 7.1.2  |                                            | 410 |

|   | 7.2  |        | Organization                               | 414 |

|   |      | 7.2.1  | The Register-to-register Data Path         | 416 |

|   |      |        | Load and Store operations                  | 417 |

|   |      |        | Jump and Branch Operations                 | 418 |

|   |      | 7.2.2  | Controlling the Single-cycle               |     |

|   |      |        | Flow-through Computer                      | 419 |

|   |      |        | Execution Time                             | 422 |

|   | 7.3  | Introd | duction to Pipelining                      | 423 |

|   |      | 7.3.1  | Speedup Ratio                              | 427 |

|   |      | 7.3.2  | Implementing Pipelining                    | 427 |

|   |      |        | From PC to Operands                        | 429 |

|   |      |        | Implementing Branch and Literal Operations | 430 |

|   |      | 7.3.3  | Hazards                                    | 434 |

|   |      |        | Delayed Branch                             | 436 |

|   |      |        | Data Hazards                               | 437 |

|   | 7.4  |        | hes and the Branch Penalty                 | 442 |

|   |      | 7.4.1  | Branch Direction                           | 443 |

|   |      | 7.4.2  | The Effect of a Branch on                  |     |

|   |      |        | the Pipeline                               | 444 |

|   |      | 7.4.3  | The Cost of Branches                       | 445 |

|   |      | 7.4.4  | The Delayed Branch                         | 448 |

|   | 7.5  | Branc  | h Prediction                               | 451 |

|   |      |        | Static and Dynamic Branch Prediction       | 453 |

|   | 7.6  | •      | mic Branch Prediction                      | 454 |

|   |      | 7.6.1  | Branch Target Buffer                       | 456 |

|   |      | 7.6.2  | Two-Level Branch Prediction                | 459 |

|   |      |        | Combining Instruction Addresses            |     |

|   | _    |        | and Branch History                         | 463 |

|   |      | mary   |                                            | 464 |

|   | Drok | lame   |                                            | 165 |

| 8 | Beyond RISC: Superscalar, VLIW, and Itanium |         |                                                     |                   |

|---|---------------------------------------------|---------|-----------------------------------------------------|-------------------|

|   |                                             |         | Overview of Chapter 8                               | 473               |

|   | 8.1                                         | Supei   | rscalar Architecture                                | 473               |

|   |                                             |         | In-Order and Out-of-Order Execution                 | 479               |

|   |                                             | 8.1.1   | Instruction Level Parallelism (ILP)                 | 482               |

|   |                                             |         | Data Dependencies and Register Renaming             | 484               |

|   |                                             | 8.1.2   | Superscalar Instruction Issue                       | 486               |

|   |                                             |         | Control Dependencies                                | 488               |

|   |                                             |         | Examples of Superscalar Processors                  | 490               |

|   |                                             |         | The Alpha                                           | 490               |

|   |                                             |         | The Pentium                                         | 492               |

|   |                                             | 8.1.3   | VLIW Processors                                     | 499               |

|   |                                             |         | Interrupts and Superscalar Processing               | 502               |

|   | 8.2                                         | Binar   | y Translation                                       | 504               |

|   |                                             |         | The IA-32 code                                      | 505               |

|   |                                             | 8.2.1   | The Transmeta Crusoe                                | 506               |

|   | 8.3                                         |         | Architecture                                        | 510               |

|   |                                             | 8.3.1   | Itanium Overview                                    | 512               |

|   |                                             |         | IA64 Assembler Conventions                          | 514               |

|   |                                             | 8.3.2   | The Itanium Register Set                            | 515               |

|   |                                             |         | The Not a Thing Bit                                 | 517               |

|   |                                             |         | Predicate and Branch Registers                      | 517               |

|   |                                             |         | Other Itanium Registers                             | 518               |

|   |                                             | 8.3.3   | IA64 Instruction Format                             | 518               |

|   |                                             | 8.3.4   | IA64 Instructions and Addressing Modes              | 519               |

|   |                                             |         | Addressing Modes                                    | 523               |

|   |                                             | 8.3.5   | Instructions, Bundles, and Breaks                   | 524               |

|   |                                             |         | IA64 Bundles, STOPs, and Assembly Language Notation | 527               |

|   |                                             | 8.3.6   | Itanium Organization                                | 529               |

|   |                                             |         | The McKinley—The Itanium 2                          | 531               |

|   |                                             |         | The Itanium 9300 Tukwila Processor                  | 532               |

|   |                                             |         | The Itanium Poulson Processor                       | 532               |

|   |                                             |         | Is the IA64 a VLIW Processor?                       | 532               |

|   |                                             | 8.3.7   | Predication                                         | 532               |

|   |                                             |         | Compare Instructions in Detail                      | 534               |

|   |                                             |         | Preventing False Data Dependency in                 |                   |

|   |                                             |         | Predicated Computing                                | 537               |

|   |                                             |         | Branch Syntax                                       | 538               |

|   |                                             | 8.3.8   | Memory Access and Speculation                       | 539               |

|   |                                             |         | Control Speculation                                 | 540               |

|   |                                             |         | The Advanced Load                                   | 541               |

|   |                                             | 8.3.9   | The IA64 and Software Pipelining                    | 543               |

|   |                                             |         | Registers and Function Calls                        | 548<br><b>549</b> |

|   |                                             | Summary |                                                     |                   |

|   | Prok                                        | olems   |                                                     | 549               |

|   |                                             |         |                                                     |                   |

## PART IV THE SYSTEM

9 Cache Memory and Virtual Memory

554

Memory Hierarchy

|    | 9.1  | Introd | luction to Cache Memory                      | 558 |

|----|------|--------|----------------------------------------------|-----|

|    |      | 9.1.1  | Structure of Cache Memory                    | 560 |

|    |      |        | Principle of Locality of Reference           | 560 |

|    | 9.2  | Perfor | mance of Cache Memory                        | 561 |

|    | 9.3  | Cache  | Organization                                 | 565 |

|    |      | 9.3.1  | Fully Associative Mapped Cache               | 566 |

|    |      |        | Associative Memory                           | 569 |

|    |      | 9.3.2  | Direct-Mapped Cache                          | 570 |

|    |      |        | Set-Associative Cache                        | 574 |

|    |      | 9.3.4  | Pseudo-Associative, Victim,                  |     |

|    |      |        | Annex, and Trace Caches                      | 579 |

|    | 9.4  | Consid | derations in Cache Design                    | 581 |

|    |      | 9.4.1  | Physical versus Logical Cache                | 581 |

|    |      | 9.4.2  | Cache Electronics                            | 582 |

|    |      | 9.4.3  | Cache Coherency                              | 582 |

|    |      | 9.4.4  | Line Size                                    | 583 |

|    |      | 9.4.5  | Fetch Policy                                 | 585 |

|    |      | 9.4.6  | Multi-Level Cache Memory                     | 586 |

|    |      | 9.4.7  | Instruction and Data Caches                  | 587 |

|    |      | 9.4.8  | Writing to Cache                             | 589 |

|    | 9.5  | Virtua | l Memory and Memory Management               | 592 |

|    |      | 9.5.1  | Memory Management                            | 592 |

|    |      | 9.5.2  | Virtual Memory                               | 595 |

|    |      |        | Memory Management and Multitasking           | 595 |

|    |      |        | Address Translation                          | 596 |

|    |      |        | Two-Level Tables                             | 598 |

|    | Sum  | mary   |                                              | 601 |

|    | Prok | olems  |                                              | 602 |

| 10 | Mai  | n Men  | nory                                         | 606 |

|    |      |        | ·                                            | 606 |

|    | 10.1 | Introd |                                              | 606 |

|    |      | 10.1.1 | Principles and Parameters of                 | 608 |

|    |      |        | Memory Systems  Rendem Access and Sequential | 000 |

|    |      |        | Random Access and Sequential Access Memory   | 608 |

|    |      |        | Volatile and Nonvolatile Memory              | 609 |

|    |      |        | Read/Write and Read-Only Memory              | 609 |

|    |      |        | Static and Dynamic Memory                    | 609 |

|    |      |        | Memory Parameters                            | 610 |

|    |      | 10 1 2 | Memory Hierarchy                             | 611 |

|    | 10.2 |        | ry Memory                                    | 612 |

|    | 10.2 |        | Static RAM                                   | 612 |

|    |      | 10.2.1 | The Static RAM Memory System                 | 615 |

|    |      |        | The Write Cycle                              | 617 |

|    |      |        | Byte/Word Control                            | 618 |

|    |      |        | Address Decoding                             | 620 |

|    |      | 10.2.2 | Interleaved Memory                           | 622 |

|    | 10.3 | DRAM   | •                                            | 623 |

|    |      |        | DRAM Timing                                  | 627 |

|    |      |        | Write-Cycle Timing                           | 630 |

|    |      |        | , ,                                          |     |

|    |      | 10.3.2 Developments in DRAM Technology            | 631 |

|----|------|---------------------------------------------------|-----|

|    |      | SDRAM                                             | 632 |

|    |      | DDR DRAM                                          | 634 |

|    |      | DDR2 and DDR3 DRAM                                | 634 |

|    |      | DDR4                                              | 636 |

|    | 10.4 | The Read-Only Memory Family                       | 637 |

|    |      | 10.4.1 The EPROM Family                           | 638 |

|    |      | The EEPROM                                        | 639 |

|    |      | Flash Memory                                      | 639 |

|    |      | Multi-Level Flash Technology                      | 640 |

|    |      | NAND and NOR Flash                                | 641 |

|    |      | Wear Leveling in Flash Memories                   | 643 |

|    | 10.5 | New and Emerging Nonvolatile Technologies         | 646 |

|    |      | 10.5.1 Ferroelectric Hysteresis                   | 648 |

|    |      | 10.5.2 MRAM-Magnetoresistive Random Access Memory | 651 |

|    |      | 10.5.3 Ovonic Memory                              | 652 |

|    | Sum  | mary                                              | 654 |

|    | Prob | lems                                              | 654 |

|    |      |                                                   |     |

| 11 | Sec  | ondary Storage                                    | 658 |

|    | 11.1 | Magnetic Disk Drives                              | 659 |

|    |      | Magnetism and Data Storage                        | 660 |

|    |      | 11.2.1 The Read/Write Head                        | 662 |

|    |      | The Recording Process                             | 663 |

|    |      | 11.2.2 Limits to Magnetic Recording Density       | 664 |

|    |      | 11.2.3 Principles of Data Recording on Disk       | 666 |

|    |      | Platter Technology                                | 670 |

|    |      | The GMR Head—A Giant Step in Read-Head Technology |     |

|    |      | Pixie Dust                                        | 672 |

|    |      | The Optically Assisted Head                       | 673 |

|    | 11.3 | Data Organization on Disk                         | 674 |

|    |      | 11.3.1 Tracks and Sectors                         | 676 |

|    |      | Formatting a Disk                                 | 678 |

|    |      | Interleaving                                      | 679 |

|    |      | 11.3.2 Disk Parameters and Performance            | 679 |

|    |      | Accessing Sectors                                 | 682 |

|    |      | The Internal Disk Cache                           | 684 |

|    |      | Transfer Rate                                     | 684 |

|    |      | 11.3.3 SMART Technology                           | 684 |

|    |      | Effect of Temperature on Disk Reliability         | 686 |

|    | 11.4 | Secure Memory and RAID Systems                    | 688 |

|    |      | RAID Level 1                                      | 689 |

|    |      | RAID Level 2 and Level 3                          | 690 |

|    |      | RAID Level 4 and Level 5                          | 691 |

|    |      | Failure of RAID 5—An Example                      | 692 |

|    |      | RAID Level 6                                      | 692 |

|    | 11.5 | Solid-State Disk Drives                           | 693 |

|    |      | Special Features of SSDs                          | 695 |

|    | 11.6 | Magnetic Tape                                     | 698 |

|    |      |                                                   |     |

|    | 11.7 | Optical Storage Technology                       | 700        |

|----|------|--------------------------------------------------|------------|

|    |      | 11.7.1 Digital Audio                             | 701        |

|    |      | 11.7.2 Reading Data from a CD                    | 702        |

|    |      | Disk Speed                                       | 705        |

|    |      | The Optical Read-Head                            | 706        |

|    |      | Focusing and Tracking                            | 706        |

|    |      | Buffer Underrun                                  | 707        |

|    |      | 11.7.3 Low-Level Data Encoding                   | 708        |

|    |      | 11.7.4 Recordable Disks                          | 711        |

|    |      | Re-Writable CDs                                  | 711        |

|    |      | Magneto-Optical Storage                          | 713        |

|    |      | 11.7.5 The DVD                                   | 714        |

|    |      | Recordable DVDs                                  | 715        |

|    |      | 11.7.6 Blu-ray                                   | 715        |

|    | Sum  | mary                                             | 717        |

|    | Prob | lems                                             | 717        |

| 12 | Inpu | ut/Output                                        | 720        |

|    | 12.1 | Fundamental Dringinles of I/O                    | 721        |

|    | 12.1 | Fundamental Principles of I/O                    |            |

|    |      | Memory-Mapped Peripherals                        | 723<br>725 |

|    |      | 12.1.1 Peripheral Register Addressing Mechanisms | 723<br>727 |

|    |      | 12.1.2 Peripheral Access and Bus Width           | 727        |

|    |      | Preserving Order in I/O Operations               |            |

|    | 12.2 | Side Effects                                     | 730        |

|    | 12.2 | Data Transfer                                    | 731        |

|    |      | 12.2.1 Open-Loop Data Transfers                  | 731        |

|    |      | 12.2.2 Closed-Loop Data Transfers                | 732        |

|    |      | 12.2.3 Buffering Data                            | 733        |

|    | 12.2 | The FIFO                                         | 734        |

|    | 12.3 | I/O Strategy                                     | 739        |

|    |      | 12.3.1 Programmed I/O                            | 739        |

|    |      | 12.3.2 Interrupt-driven I/O                      | 740        |

|    |      | Interrupt Processing                             | 741        |

|    |      | Nonmaskable Interrupts                           | 742        |

|    |      | Prioritized Interrupts                           | 742        |

|    |      | Nested Interrupts                                | 743        |

|    |      | Vectored Interrupts                              | 745        |

|    |      | Interrupt Timing                                 | 746        |

|    |      | 12.3.3 Direct Memory Access                      | 749        |

|    |      | Performance of I/O Systems                       | 751        |

|    | 12.5 | The Bus                                          | 752        |

|    |      | 12.5.1 Bus Structures and Topologies             | 753<br>755 |

|    |      | 12.5.2 The Structure of a Bus                    | 755        |

|    |      | The Data Bus                                     | 756        |

|    |      | Bus Speed                                        | 756        |

|    |      | The Address Bus                                  | 759        |

|    | _    | The Control Bus                                  | 760        |

|    | 12.6 | Arbitrating for the Bus                          | 761        |

|    |      | 12.6.1 Localized Arbitration and the VMEbus      | 763        |

|    |      | Releasing the Bus                                | 766        |

|         |        | The Arbitration Process               | 766 |

|---------|--------|---------------------------------------|-----|

|         |        | VMEbus Arbitration Algorithms         | 767 |

|         | 12.6.2 | Distributed Arbitration               | 768 |

|         |        | NuBus Arbitration                     | 768 |

| 12.7    | The PO | 772                                   |     |

|         | 12.7.1 | The PCI Bus                           | 772 |

|         |        | Data Transactions on the PCI Bus      | 776 |

|         | 12.7.2 | The PCI Express Bus                   | 781 |

|         |        | PCIe Data Link Layer                  | 784 |

|         | 12.7.3 | CardBus, the PC Card, and ExpressCard | 785 |

|         |        | CardBus Cards                         | 787 |

|         |        | ExpressCard Cards                     | 788 |

| 12.8    | The SC | 789                                   |     |

|         |        | SCSI Signals                          | 790 |

|         |        | SCSI Bus Transactions                 | 792 |

|         |        | SCSI Messages and Commands            | 792 |

| 12.9    | Serial | 794                                   |     |

|         | 12.9.1 | The Ethernet                          | 795 |

|         | 12.9.2 | FireWire 1394 Serial Bus              | 797 |

|         |        | Serial Bus Addressing                 | 800 |

|         |        | The Physical Layer                    | 800 |

|         |        | Arbitration                           | 803 |

|         |        | Initialization                        | 804 |

|         |        | The Link Layer                        | 804 |

|         | 12.9.3 | USB                                   | 805 |

|         |        | USB – The First Two Generations       | 805 |

|         |        | Electrical Characteristics            | 806 |

|         |        | Physical Layer Data Transmission      | 808 |

|         |        | Logical Layer                         | 809 |

|         |        | USB 3.0                               | 811 |

| Summary |        |                                       | 812 |

| Prob    | lems   |                                       | 813 |

|         |        |                                       |     |

| "115°C (T)   - | PART V | PROCESSOR-LEVEL PARALLELISM                         |     |

|----------------|--------|-----------------------------------------------------|-----|

| (26) 5         | TANT   | THOCESSON LEVEL I ANALLELISM                        |     |

|                | 13     | Processor-Level Parallelism                         | 820 |

|                |        | Dimensions of Parallel Processing                   | 822 |

|                |        | A Brief History of Parallel Computing               | 823 |

|                |        | 13.1 Why Parallel Processing?                       | 825 |

|                |        | 13.1.1 Power—The Final Frontier                     | 826 |

|                |        | 13.2 Performance Revisited                          | 829 |

|                |        | Performance Measurement                             | 831 |

|                |        | 13.3 Flynn's Taxonomy and Multiprocessor Topologies | 833 |

|                |        | 13.4 Multiprocessor Topologies                      | 835 |

|                |        | 13.5 Memory in Multiprocessor Systems               | 842 |

|                |        | 13.5.1 NUMA Architectures                           | 842 |

|                |        | 13.5.2 Cache Coherency in Multiprocessor Systems    | 843 |

|                |        | The MESI Protocol                                   | 844 |

|                |        | False Sharing                                       | 847 |

| 13.6         | Multithreading        |                                          |     |  |

|--------------|-----------------------|------------------------------------------|-----|--|

| 13.7         | Multi-core Processors |                                          |     |  |

|              |                       | Homogeneous and Heterogeneous Processors | 852 |  |

|              | 13.7.1                | Homogeneous Multiprocessors              | 852 |  |

|              |                       | Intel Nehalem Multi-Core Processor       | 854 |  |

|              |                       | AMD Multi-Core Processors                | 854 |  |

|              |                       | ARM Cortex A9 Multi Core                 | 856 |  |

|              |                       | IBM Power7                               | 857 |  |

|              |                       | The GPU                                  | 858 |  |

|              | 13.7.2                | Heterogeneous Multiprocessors            | 861 |  |

|              |                       | The Cell Architecture                    | 861 |  |

|              | 13.7.3                | Networks on a Chip                       | 862 |  |

| 13.8         | Paralle               | 865                                      |     |  |

|              | 13.8.1                | Parallel Processing and Programming      | 867 |  |

|              |                       | OpenMP                                   | 868 |  |

|              | 13.8.2                | Message Passing Interface                | 870 |  |

|              | 13.8.3                | Partitioned Global Address Space         | 871 |  |

|              | 13.8.4                | Synchronization                          | 872 |  |

|              |                       | The Spinlock                             | 873 |  |

| Sum          | Summary               |                                          |     |  |

| Problems     |                       |                                          |     |  |

| Bibliography |                       |                                          | 876 |  |

| Index        |                       |                                          |     |  |

# **Preface**

The twenty-first century is an age of scientific and technological wonders. Computers have proved to be everything people expected—and more. Bioengineering has unraveled the mysteries of the cell and enabled scientists to synthesize drugs that were inconceivable a decade ago. Nanotechnology provides a glimpse into a world where the computer revolution is combined with engineering at the atomic level to create microscopic autonomous machines that may, one day, be injected into the body to carry out internal repairs. Ubiquitous computing has given us cell phones, MP3 players, and digital cameras that keep us in touch with each other via the Internet. The computer is at the core of almost all modern technologies. This book explains how the computer works.

The discipline called *computing* has been taught in universities since the 1950s. In the beginning, computing was dominated by the large mainframe, and the subject consisted of a study of computers themselves, the operating systems that controlled the computers, languages and their compilers, databases, and business computing. Since then, computing has expanded exponentially and now embraces so many different areas that it's impossible for any university to cover computing in a comprehensive fashion. We have to concentrate on the essential elements of computing. At the heart of this discipline lies the machine itself: the computer. Of course, computing as a theoretical concept could exist quite happily without computers. Indeed, a considerable amount of work on the theoretical foundations of computer science was carried out in the 1930s and 1940s before the computer revolution took place. However, the way in which computing has progressed over the last 40 years is intimately tied up with the rise of the microprocessor. The Internet could not have taken off in the way it has if people didn't have access to very low-cost computers.

Since the computer itself has had such an effect on both the growth of computing and the path computing has taken, it's intuitively reasonable to expect that the computing curriculum should include a course on how computers actually work. University-level Computer Science and Computer Engineering CS programs invariably include a course on how computers work. Indeed, professional and course accreditation bodies specify computer architecture as a core requirement; for example, computer architecture is central to the joint IEEE Computer Society and ACM Computing Curriculum.

Courses dealing with the embodiment or realization of the computer are known by a variety of names. Some call them hardware courses, some call them computer architecture courses, and some call them computer organization courses (with all manner of combinations in between). Throughout this text, I will use the expression *computer architecture* to describe the discipline that studies the way in which computers are designed and how they operate. I will, of course, explain why this discipline has so many different names and point out that the computer can be viewed in different ways.

Like all areas of computer science, the field of computer architecture is advancing rapidly as developments take place in instruction set design, instruction level parallelism, cache memory technology, bus systems, speculative execution, multi-core computing, and so on. We examine all these topics in this book.

Computer architecture underpins computer science; for example, computer performance is of greater importance today than ever before, because even those who buy personal computers have to understand systems architecture in order to make the best choice.

Although most students will never design a new computer, today's students need a much broader overview of the computer than their predecessors. Students no longer have to be competent assembly language programmers, but they must understand how buses, interfaces, cache memories, and instruction set architectures determine the performance of a computer system.

Moreover, students with an understanding of computer architecture are better equipped to study other areas of computer science; for example, a knowledge of instruction set architectures gives students a valuable insight into the operation of compilers.

My motivation for writing this book springs from my experience in teaching an intermediate level course in computer architecture at the University of Teesside. I threw away the conventional curriculum that I'd inherited and taught what could be best described as *Great Ideas in Computer Architecture*. I used this course to teach topics that emphasized global concepts in computer science that helped my students with both their operating systems and C courses. This course was very successful, particularly in terms of student motivation.

Anyone writing a text on computer architecture must appreciate that this subject is taught in three different departments: electrical engineering (EE), electrical and computer engineering (ECE), and computer science (CS). These departments have their own cultures and each looks at the computer from their own viewpoint. EE and ECE departments focus on electronics and how the individual components of a computer operate. EE/ECE-oriented texts concentrate on gates, interfaces, signals, and computer organization. Many students in CS departments don't have the requisite background in electronics, so they can't follow texts that emphasize circuit design. Instead, computer science departments place more stress on the relationship between the low-level architecture of the processor and the higher-level abstractions in computer science.

Although it is near impossible to write a text optimized for use in both EE/ECE and CS departments, *Computer Organization and Architecture: Themes and Variations* is an effective compromise that provides sufficient detail at the logic and organizational levels for EE/ECE departments without including the degree of detail that would alienate CS readers.

Undergraduate computer architecture is taught at three levels: introductory, intermediate, and advanced. Some schools teach all three levels, some compress this sequence into two levels, and some provide only an introduction. This text is aimed at students taking first- and second-level courses in computer architecture and at professional engineers who would like an overview of current developments in microprocessor architecture. The only prerequisite is that the reader should be aware of the basic principles of a high-level language such as C and have a knowledge of basic algebra.

It is difficult to pitch a book at precisely the right level. Indeed, such an ideal level doesn't exist. Different students react in different ways to any specific text. If you make a book very focused and follow a narrow curriculum, you appeal only to students on a tiny handful of courses. Computer Organization and Architecture: Themes and Variations is well-suited to a wide range of courses, because it covers the basics and some of the more advanced topics in computer architecture.

### **Features of the Book**

Why inflict yet another text on computer architecture on the world? Computer architecture is a fascinating topic. It's all about how you can take vast numbers of a single primitive element such as a NAND gate and make a computer. It's all about how common sense and technology meet. For example, the cache memory that makes processors so fast is conceptually no more complicated than the note on the back of an envelope. Equally, the way in which all processors operate uses a technique invented by Ford for car production: the *pipeline* or production line. I have tried to make the subject interesting and have covered a greater range of topics than absolutely necessary. For example, in this text we will look at memory devices that operate by moving an oxygen atom from one end of a crystal to the other.

The title of this text, Computer Organization and Architecture, emphasizes the structure of the complete computer system (CPU, memory, buses, and peripherals). The subtitle Themes and Variations indicates that there is a theme (i.e., the computer system) and also variations, for example, the different approaches to increasing the speed of a CPU or to organizing cache memory.

It is often easier to describe something in terms of what it isn't rather than what it is. This book is not concerned with the precise engineering details of microprocessor systems design, interfacing, and peripherals. It certainly isn't an assembly language primer. The central theme of this book is microcomputer *architecture* rather than microprocessor systems design. Computer architecture can be defined, for our present purposes, as the view of a computer seen by the machine language programmer. That is, a computer's architecture takes no account of its actual hardware or implementation and is concerned only with what it does. We will not consider some of the hardware and interfacing aspects of microprocessors, except where they impinge on its architecture (e.g., cache memory, memory management, and the bus).

#### The Target Architecture

Anyone writing an architecture text has to select a target architecture as a vehicle to teach the fundamentals of machine design and assembly language programming. Professors regularly debate with religious intensity the relative merits of illustrating a course with a real commercial processor or with a hypothetical generic processor. The generic machine is easy to understand and has a shallow learning curve. Students often find that absorbing the fine details of a real processor is time consuming and unrewarding. On the other hand, practical engineering is all about living with the limitations of the real world. Moreover, a real machine teaches students about the design decisions that engineers have to make in order to create a commercially viable product.

In the 1970s and 1980s DEC's PDP-11 minicomputer was widely adopted as a teaching vehicle. The PDP-11 gradually dropped out of the curriculum with the advent of 16-bit microprocessors such as the Motorola 68K. From the academic's point of view, the 68K (loosely based on the earlier PDP-11) was a dream machine, because its architecture is relatively regular and that made it easy for students to write programs in 68K assembly language. A casual observer might have expected the ubiquitous Intel IA32 family, which is found in most PCs, to have played a significant role in computer architecture education. After all, countless students get hands-on experience of Intel's processors. The 80x86 family has never really caught on in the academic world because its complex architecture grew in an ad-hoc fashion as each new member of the family was released and this presents students with an excessive burden. Some academics illustrate their course with a high-performance RISC processor, such as MIPS, which is both powerful and easy to understand. Such high-end RISC processors are found in workstations but are relatively unknown to many students (professors have observed that students often request PC-based technology due to their familiarity with the PC). However, RISC processors are used in both high-performance computers and most cell phones.

I have selected the ARM processor as a vehicle to introduce assembly language and computer organization. It is a processor that is powerful, elegant, yet easy to learn. Moreover, development tools for the ARM processor are widely available which means that students can write programs in ARM assembly language and run them in the lab or at home on their PCs.

A strong contender for the role of target architecture in a modern text is Intel's IA64 Itanium processor. This is a device of immense power and sophistication, yet its basic architecture is simpler than the 80x86 family. The rich and innovative features of the Itanium's architecture illustrate numerous concepts found in a computer architecture course–from the data stack to speculative execution, and from pipelining to instruction level parallelism (ILP). Consequently, I also introduce some features of this processor when we look at high-performance computing.

Computer Organization and Architecture: Themes and Variations isn't a conventional computer architecture text. I go beyond the conventional curriculum and cover material that is interesting, important, and relevant. One of my principal objectives is to provide students with an appropriate body of knowledge that they can absorb. All too often, students graduate from university with embarrassingly large gaps in their knowledge. I know of no other text that adopts my approach. For example, all computer architecture texts introduce floating-point arithmetic, yet very few discuss the codes for data compression required to store large volumes of textual and video information, and none describe the MP3 data compression that's at the heart of an entire industry. Similarly, computer architecture texts often lack

coverage of architectural features intended to support multimedia applications. Some of the highlights of this text are described below.

#### History

Books on computer architecture usually have a section on the history of the computer. Such history chapters are often inaccurate and have received criticism from experts in the field. However, I feel that a history chapter is important, because a knowledge of computer history helps students appreciate how and why developments took place. By knowing where computers came from, students are better able to understand how they are likely to develop in the future. In this text, I provide a short overview of the history of computing and include further historical background in the supplementary web-based material that accompanies this book.

#### **OS Support**

The operating system is intimately bound up with computer architecture. Computer Organization and Architecture: Themes and Variations covers topics in architecture of interest to those who also study operating systems (e.g., memory management, context switching, protection mechanisms).

#### Multimedia Support

The most important driving force behind modern computer architectures is the growth of multimedia systems with their insatiable demand for high performance and high bandwidths. This text demonstrates how modern architectures have been optimized for multimedia applications. We look at the effect of multimedia applications on both the architectures of computers and the design of buses and computer peripherals, such as hard disks for use in audiovisual applications.

## Input/Output Systems

Today's computers are not only much faster than their predecessors, but they also provide more sophisticated means of getting information into and out of the computer. I/O was of relatively little importance when the typical computer was interfaced only to a keyboard, modem, and printer. Computers are now routinely interfaced to peripherals, such as digital video cameras that demand massive data transfer rates. We will look at some of the modern, high-performance I/O systems, such as the USB and FireWire interfaces. We will also delve more deeply into input/output-related topics such as handshaking and buffering.

#### Computer Memory Systems

Memory is the *Cinderella* of the computer world. Without high-density, high-performance memory systems, neither low-cost desktop systems nor digital cameras with 32GB of storage would be possible. I have divided memory systems into two chapters: the first dealing with semiconductor memory and the second dealing with magnetic and optical memory. We will also take a look at some of the interesting emerging memory technologies, such as Ovonic memory and ferroelectric memory.

# **Approach**

The books that I've most enjoyed are those where a little of the author's personality and view of the subject shines through. I hope that the same is true of this book. Computer architecture isn't something that can be expressed as a set of cold equations to be learned; it is a culture

that has developed over the years. At conferences, you will meet academics who passionately argue the relative merits of this computer over that one. I would be a poor educator if I did not at least hint to students that computer architecture can be as much fad as fact.